#### US006854116B1

## (12) United States Patent

Anderson et al.

## (10) Patent No.: US 6,854,116 B1

(45) **Date of Patent:** Feb. 8, 2005

# (54) EXECUTION CONTROL FOR PROCESS

(75) Inventors: Eric C. Anderson, San Jose, CA (US); Hugh B. Svendsen, Atlanta, GA (US)

(73) Assignee: Apple Computer, Inc., Cupertino, CA

(US)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

(21) Appl. No.: 09/007,019

(22) Filed: Jan. 14, 1998

#### Related U.S. Application Data

(63) Continuation of application No. 08/478,413, filed on Jun. 7, 1995, now abandoned, which is a continuation of application No. 07/954,970, filed on Sep. 30, 1992, now Pat. No. 6,304,891.

| (51) | Int. Cl. <sup>7</sup> | <br>G06F 9/00 |

|------|-----------------------|---------------|

| (52) | U.S. Cl.              | <br>718/100   |

|      |                       | <br>          |

### (56) References Cited

### U.S. PATENT DOCUMENTS

| 4,954,948 | A  | * | 9/1990  | Hira et al     | 364/200 |

|-----------|----|---|---------|----------------|---------|

| 5,283,900 | Α  | * | 2/1994  | Frankel et al  | 395/700 |

| 5,325,526 | Α  | * | 6/1994  | Cameron et al  | 395/650 |

| 5,448,735 | Α  | * | 9/1995  | Anderson et al | 395/650 |

| 5,553,309 | Α  | * | 9/1996  | Asai et al     | 395/854 |

| 6.304.891 | B1 | * | 10/2001 | Anderson et al | 709/107 |

#### € 600 DSPGlobals 601 DSPDevice - 604 DSPClient 621a < 621 Real-Time Task List DSPModule DSPModule DSPModule DSPTask 611 DSPSection(s) DSPSection(s) 610 - 624 DSPModule DSPTask 612 - 625 DSPModule DSPModule DSPTask 613 DSPSection(s) **627** DSPModule DSPTask 614 DSPSection(s) DSPModule DSPTask 631 DSPSection(s) - 637 DSPModule DSPModule DSPTask 632 DSPSection(s) DSPSection(s) DSPSection(s) - 639 640 DSPModule DSPModule DSPSection(s) DSPSection(s)

#### OTHER PUBLICATIONS

Digital Equipment Corporation, Open VMS I/O User's Reference Manual, Mar., 1994, pp. 3–16 to 3–17.\*

\* cited by examiner

Primary Examiner—Sue Lao (74) Attorney, Agent, or Firm—Blakely, Sokoloff, Taylor & Zafman LLP

### (57) ABSTRACT

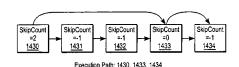

Method and means for controlling the execution sequence of a first sequence of modules in a first task. The first sequence of modules are linked to one another and have at least one sequence of execution. The method stores in each of the first sequence of modules a skip value representing which of subsequent modules to execute. The method executes the first of the first sequence of said modules, and then executes the next of the modules indicated by the skip value. Conservation of processor bandwidth is accomplished by avoiding the loading of modules which will not be executed.

Method and means are further provided for simultaneous activation/deactivation of a set of tasks by a processor, each of the tasks normally executed in a sequential fashion by one or more processors. A list of tasks to be activated/deactivated is stored, including the timing relationship for the activation process. The list is then implemented as frame numbers for activation and requested state in the actual task list. The executing processor compares the requested state to the actual state for each task, and if different, compares the value of the activation frame with the current frame. If the current frame equals or exceeds the activation frame, then the requested active state is transferred to the actual state.

#### 26 Claims, 18 Drawing Sheets